Новейшая Технология AMD 3D V-Cache Использует Микросоединения в 9 Микрон

На конференции Hot Chips 33 AMD представила свое решение 3D V-Cache, которое должно стать важной вехой в разработке их процессоров с архитектурой Zen, и не только.

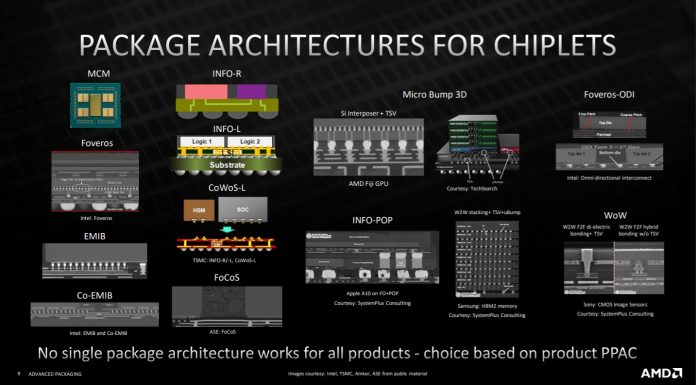

Презентация AMD позволила нам вспомнить все технологии этого типа, позволяющие наращивать интегральные схемы. В настоящее время наиболее популярным способом независимого соединения отдельных слоев в процессорах или модулях памяти является TSV (Through Silicon Via). Это метод соединения отдельных слоев с помощью микроподключений (мостов), количество которых определяет скорость передачи и ее стабильность.

Решение AMD в случае соединений TSV – это использование соединений с интервалом 9 микрон, что должно конкурировать с техникой Intel Foveros Direct, основанной на соединениях с интервалом 10 микрон.

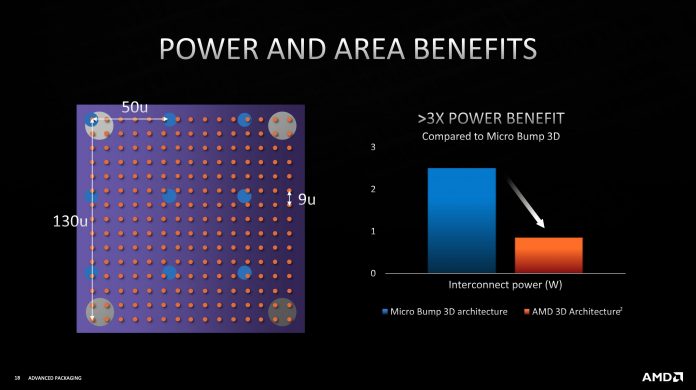

AMD прогнозирует, что их последняя технология 3D Chiplet, использующая 9-микронные соединения, будет в 3 раза более энергоэффективной, а плотность соединений увеличится в пятнадцать раз.

Первыми процессорами, которые выиграют от этого типа стекирования полупроводниковых систем, будут процессоры AMD, использующие архитектуру Zen3, а именно AMD Ryzen 9 5900X, который должен получить кэш L3 большего размера на 64 МБ.